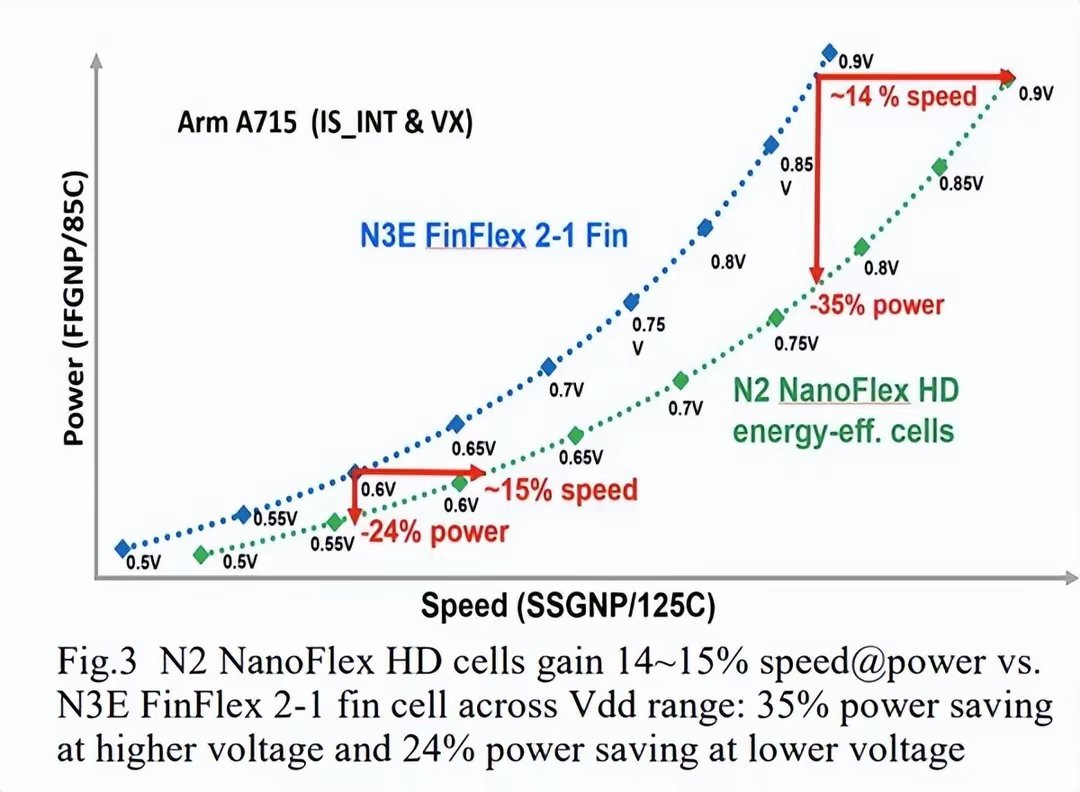

在2024年IEDM大會上,臺積電首次揭示了其2nm工藝的核心技術細節及性能指標,展示了該工藝相比3nm技術的顯著進步。具體來說,臺積電2nm的晶體管密度較3nm增加了15%,同時在相同功耗下,性能提升了15%。更為重要的是,在保持同等性能的情況下,功耗可降低24%至35%。

臺積電2nm工藝首次引入了全環繞柵極(GAA)納米片晶體管。這一創新技術能夠通過精確調節通道寬度,在提升性能的同時顯著優化能效。通過納米片結構,增強了晶體管的電流控制,確保其在低電壓下也能高效運行。

此外,臺積電還在其2nm工藝中加入了NanoFlex DTCO(設計技術聯合優化)。這一技術能夠根據不同需求,靈活調整芯片的尺寸和性能。設計師可以在功耗和性能之間找到最佳平衡,進一步提升集成度和能效。

另一個顯著的技術突破是臺積電2nm工藝採用了第三代偶極子集成,結合N型和P型納米片晶體管,支持六個電壓閾值檔位(6-Vt),這意味著更廣泛的電壓範圍和更高的靈活性。通過這些改進,N型和P型晶體管的I/CV速度分別提升了70%和110%,為高性能計算提供了強大支持。

與傳統FinFET工藝相比,臺積電2nm工藝的納米片晶體管在低電壓下也能夠獲得更優的能效。具體來說,在0.5V到0.6V的電壓下,新工藝能將頻率提高20%左右,同時待機功耗可降低約75%。

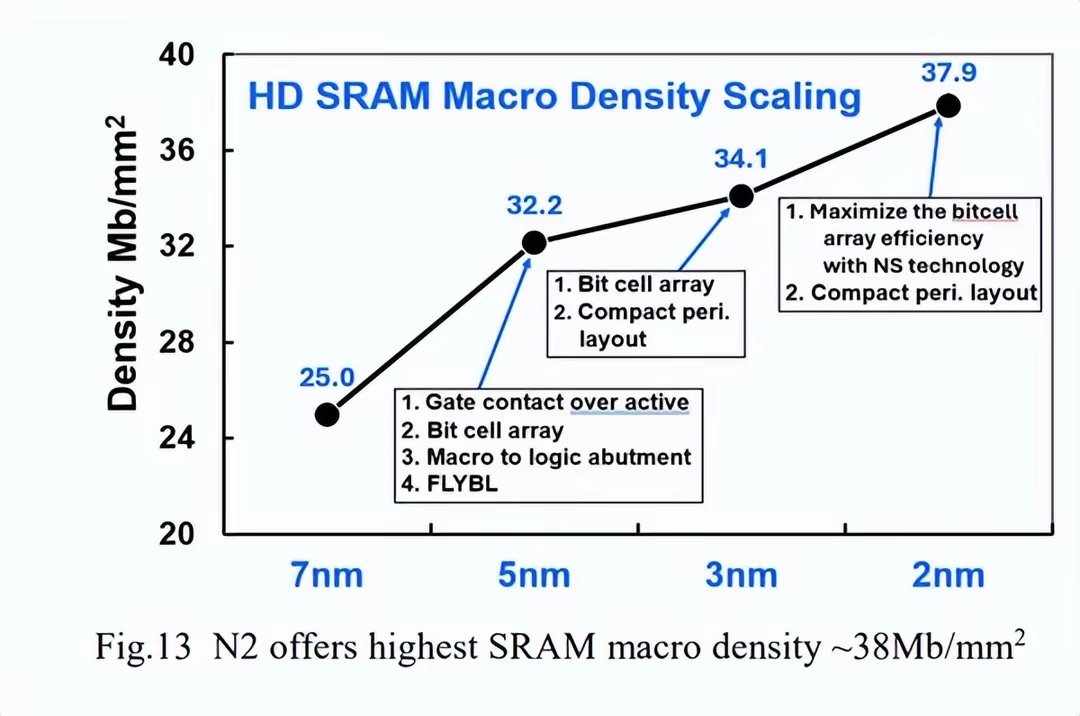

在存儲技術方面,臺積電2nm工藝也表現不凡,SRAM密度突破至每平方毫米38Mb,創下新紀錄,滿足了日益增長的存儲需求。

除此之外,臺積電還對金屬層工藝進行了優化,首次採用了一步蝕刻(1P1E)和一次EVU曝光技術,大幅降低了工藝複雜度並減少了光罩數量。

針對高性能計算領域,臺積電引入了超高性能的SHP-MiM電容。每平方毫米約200fF的電容容量使得新工藝能夠支持更高的運行頻率,進一步提升了其計算性能。

根據臺積電的介紹,自28nm工藝問世以來,臺積電在工藝性能上的提升已超過140倍,2nm工藝的創新再次證明了其在全球半導體領域的領導地位。