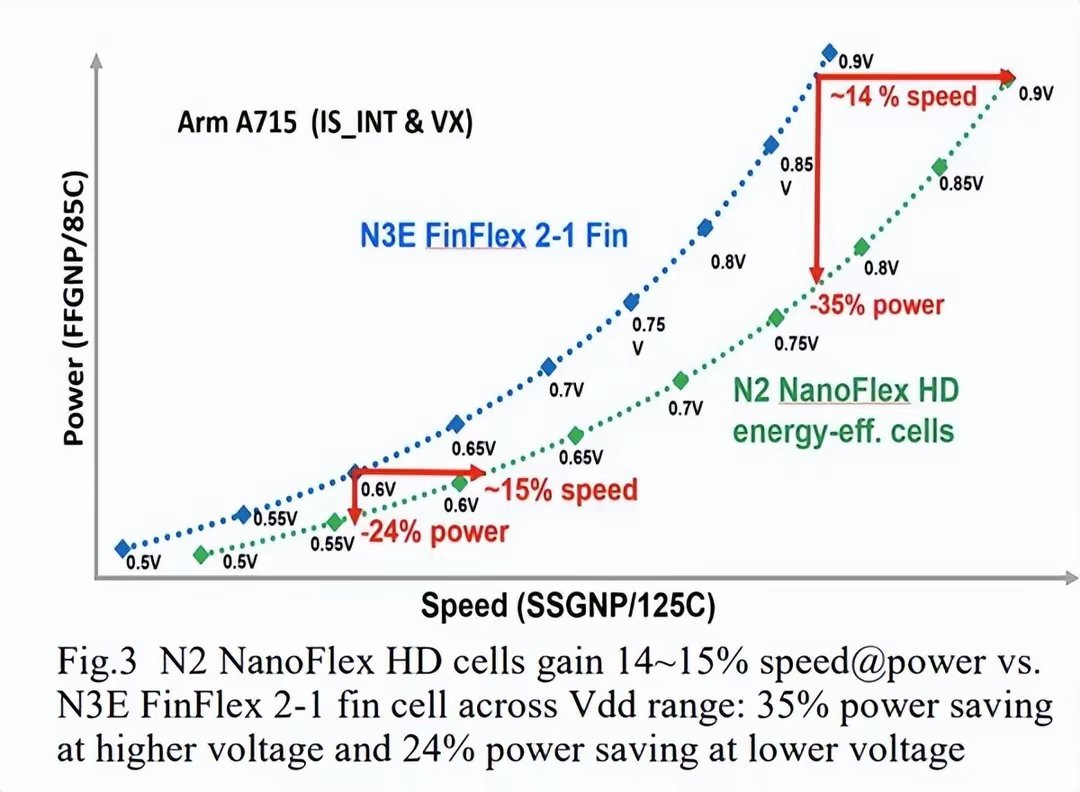

在2024年IEDM大会上,台积电首次揭示了其2nm工艺的核心技术细节及性能指标,展示了该工艺相比3nm技术的显著进步。具体来说,台积电2nm的晶体管密度较3nm增加了15%,同时在相同功耗下,性能提升了15%。更为重要的是,在保持同等性能的情况下,功耗可降低24%至35%。

台积电2nm工艺首次引入了全环绕栅极(GAA)纳米片晶体管。这一创新技术能够通过精确调节通道宽度,在提升性能的同时显著优化能效。通过纳米片结构,增强了晶体管的电流控制,确保其在低电压下也能高效运行。

此外,台积电还在其2nm工艺中加入了NanoFlex DTCO(设计技术联合优化)。这一技术能够根据不同需求,灵活调整芯片的尺寸和性能。设计师可以在功耗和性能之间找到最佳平衡,进一步提升集成度和能效。

另一个显著的技术突破是台积电2nm工艺采用了第三代偶极子集成,结合N型和P型纳米片晶体管,支持六个电压阈值档位(6-Vt),这意味着更广泛的电压范围和更高的灵活性。通过这些改进,N型和P型晶体管的I/CV速度分别提升了70%和110%,为高性能计算提供了强大支持。

与传统FinFET工艺相比,台积电2nm工艺的纳米片晶体管在低电压下也能够获得更优的能效。具体来说,在0.5V到0.6V的电压下,新工艺能将频率提高20%左右,同时待机功耗可降低约75%。

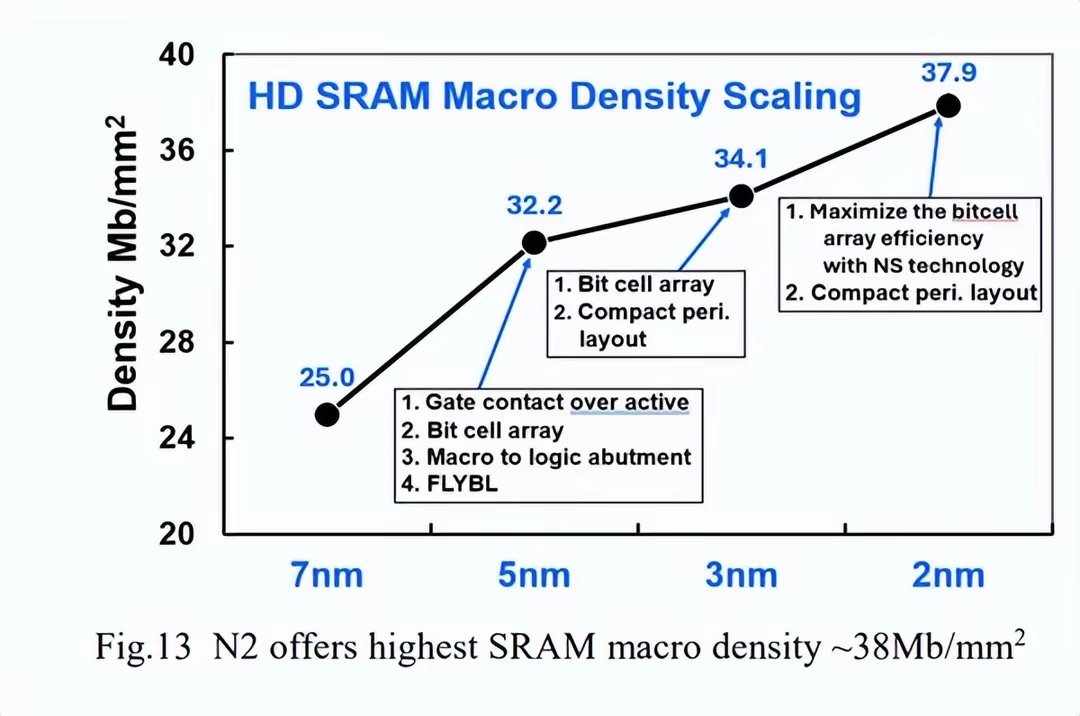

在存储技术方面,台积电2nm工艺也表现不凡,SRAM密度突破至每平方毫米38Mb,创下新纪录,满足了日益增长的存储需求。

除此之外,台积电还对金属层工艺进行了优化,首次采用了一步蚀刻(1P1E)和一次EVU曝光技术,大幅降低了工艺复杂度并减少了光罩数量。

针对高性能计算领域,台积电引入了超高性能的SHP-MiM电容。每平方毫米约200fF的电容容量使得新工艺能够支持更高的运行频率,进一步提升了其计算性能。

根据台积电的介绍,自28nm工艺问世以来,台积电在工艺性能上的提升已超过140倍,2nm工艺的创新再次证明了其在全球半导体领域的领导地位。