不知不覺樓主鴿了很長時間呢,本篇我們主要講

不知不覺樓主鴿了很長時間呢,本篇我們主要講

1.狀態顯示

狀態顯示是我們構築組合邏輯電路的基礎。在現實電路中,狀態顯示有高電平,低電平,非法值,浮空值。但在泰拉瑞亞中只有兩種狀態顯示,對應高電平和低電平。在泰拉瑞亞中,我們用邏輯燈的亮滅來表示輸入的狀態。在這裡,為了方便教學,我們規定邏輯燈亮為1,邏輯燈滅為0.

如圖:

2.邏輯門的結算順序

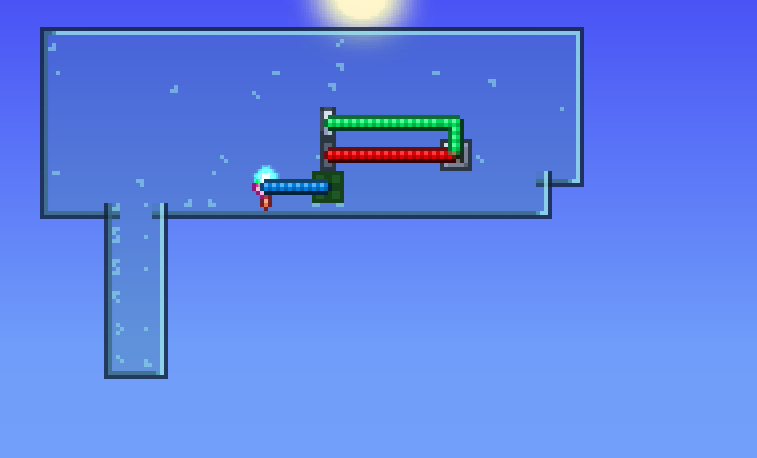

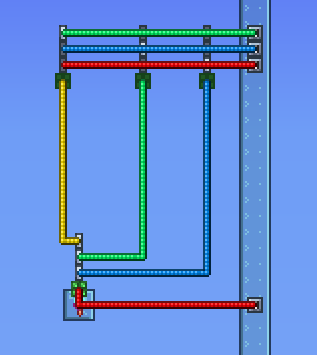

在泰拉瑞亞中,邏輯門發出信號看似沒有延遲,全部在一物理幀內完成,但邏輯門確實有其運算順序,我們可以通過以下電路來證明:

如圖,當我拉下開關時,紅線和綠線都被激活,但與門上邏輯燈仍是一亮一滅,因此與門不會發出信號,火把狀態不改變。

如圖,當我拉下開關時,紅線和綠線都被激活,但與門上邏輯燈仍是一亮一滅,因此與門不會發出信號,火把狀態不改變。 但是當我在綠線上加裝一個與門後,效果就變得不一樣了,火把可以被激活。

但是當我在綠線上加裝一個與門後,效果就變得不一樣了,火把可以被激活。

如圖,火把能被被激活是因為與門a1在a2打開上面的邏輯燈前先一步關掉了下面的邏輯燈,與門a1在瞬間完成亮滅切換,發出信號。那麼現在,來說一下泰拉瑞亞中電路的結算機制。

如圖,火把能被被激活是因為與門a1在a2打開上面的邏輯燈前先一步關掉了下面的邏輯燈,與門a1在瞬間完成亮滅切換,發出信號。那麼現在,來說一下泰拉瑞亞中電路的結算機制。1.電線的激活順序為紅,藍,綠,黃(雖然在遊戲中無法體現和證明,影響不大,可以忽略不計,但是可以藉助

MechScope模組鏡像站下載鏈接,有需要的自取

2.只要是邏輯門,都遵守逐級結算的順序(不論任何邏輯門都是如此)

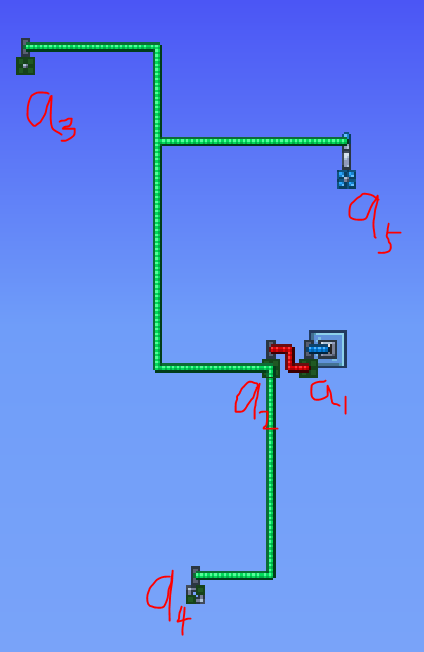

這裡舉一個例子,如圖:

與門a1在第一級,最早結算,與門a2在第二級,故第二個結算,與門a3,或門a4,故障門a5都在第三級,所以同時最晚結算。

與門a1在第一級,最早結算,與門a2在第二級,故第二個結算,與門a3,或門a4,故障門a5都在第三級,所以同時最晚結算。知道了這些後,我們就可以正式進入組合邏輯了。

2.認識組合邏輯

組合邏輯電路是指在任何時刻,輸出狀態只決定於同一時刻各輸入狀態的組合,而與電路以前狀態無關,而與其他時間的狀態無關。請注意輸出狀態只決定於同一時刻各輸入狀態。

在泰拉瑞亞中,組合邏輯的構築一般只需要與門和異或門。

不是說電路必須在同級結算,而是每一步電路間不能相互影響。

3.構建組合邏輯電路

(1)真值表

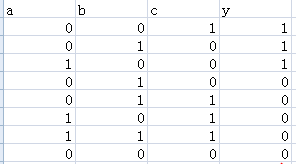

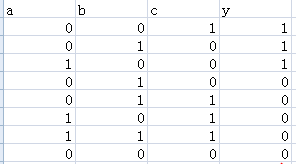

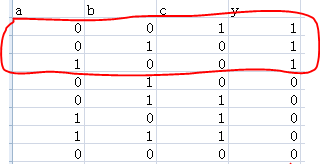

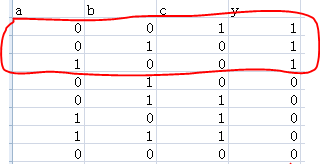

真值表是表徵邏輯事件輸入和輸出之間全部可能狀態的表格,我們通常令1為真,0為假。比如下面這個:

如圖,abc為輸入,y為輸出,既然我們要構建組合邏輯電路,就必須依據這個寫出邏輯表達式。

(2)邏輯表達式用邏輯運算符將關係表達式或邏輯量連接起來的有意義的式子稱為邏輯表達式。如何才能有意義,是需要構建電路的人去規定的,所謂的“有意義”是指輸出的值。如果你現在看不懂的話,不用擔心,後文我們會給出具體例子進一步教學。

現在說一下邏輯運算符的種類。

能用到的就這幾個:

ab:表示項a和項b通過與門進行輸出,也可以寫作a∩b

a+b:表示項a和項b通過或門進行輸出,也可以寫作a∪b,在遊戲中我們可以用與門來替換

a⊕b:表示項a和項b通過異或門進行輸出

a':表示項a的取反,也表示項a通過非門輸出,也可以寫作¬a或者!或者a上劃線(我打不出來你們自行想象吧)在泰拉瑞亞中,我們可以通過單次信號的激活來取反

那麼我們該如何寫出邏輯表達式呢?

例1:根據上圖中真值表寫出邏輯表達式

例1:根據上圖中真值表寫出邏輯表達式在這裡,我們默認輸入為1時正常,取0時則為取反符,如:當a輸入為0時,則表示為a'

我們默認y取1時有意義,也就是說,我們只需要列出當y=1時的邏輯表達式,如圖:

邏輯表達式為y=a'b'c+a'bc'+ab'c',形如這樣的邏輯表達式叫與或式

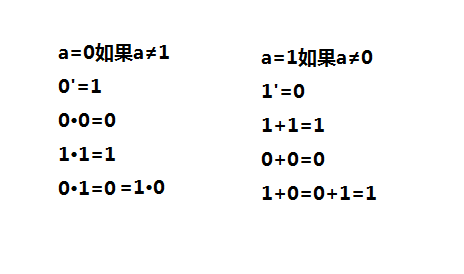

邏輯表達式為y=a'b'c+a'bc'+ab'c',形如這樣的邏輯表達式叫與或式簡單的邏輯運算法則如下:

值得注意的是,某些邏輯表達式可以被化簡,至於化簡方法...就請自行查閱吧,這涉及太多數電的知識了

如果實在想化簡的話可以藉助下面這兩個網站

Online Karnaugh map solver with circuit for up to 6 variables (32x8.com)

mathematical-logic-workstation (gitee.io)

(3)在遊戲中構造電路

這裡我們仍以y=a'b'c+a'bc'+ab'c'為例,真值表如下

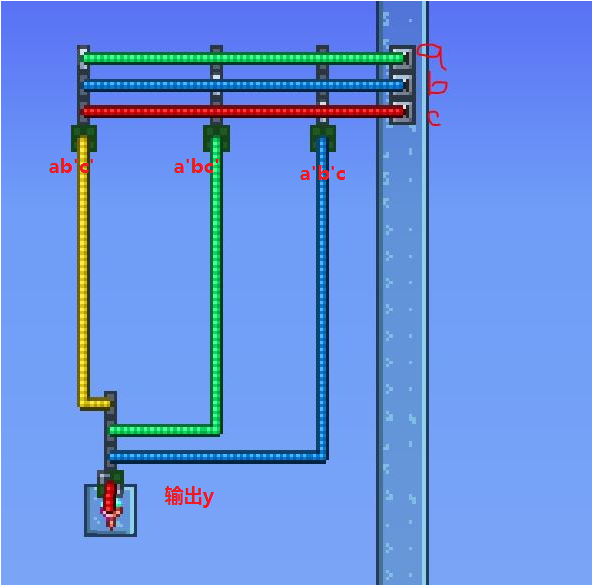

我們這裡要嚴格按照真值表和邏輯表達式擺邏輯燈和邏輯門,效果如下

我們這裡要嚴格按照真值表和邏輯表達式擺邏輯燈和邏輯門,效果如下

如圖,一個組合邏輯電路就完成了,這裡的電線作用是取反以及賦值。這裡就需要我們提到的邏輯運算法則了,圖中狀態是111,也就是全開,三個與門各輸出一次信號,在或門處,總輸出為1(圖中火把亮為1)(即y=1+1+1=1,)按照真值表,當且僅當符合a,b,c中其中只有一個為1時火把被激活。效果如下:

當然,圖中的或門也可以用與門替換

當然,圖中的或門也可以用與門替換

課後作業:7端數碼管顯示譯碼器的製作(數顯)課後作業度盤鏈接提取碼:tapW

後續樓主會在這裡給出參考答案

如有錯誤歡迎指正